Noise Analysis of a 434-MHz Wakeup Receiver Analog Frontend Core With −93-dBm Input Sensitivity and 65-pJ/Bit Efficiency Based on a Switched Injection-Triggered Oscillator With Surface Acoustic Wave Resonator

Abstract

DOI: 10.1109/TMTT.2024.3482456

IEEEXplore: https://ieeexplore.ieee.org/document/10745803

Device

Wakeup receiver analog frontend core in GlobalFoundaries 22 nm FD-SOI technology

Spectrum

434 MHz

Novelty

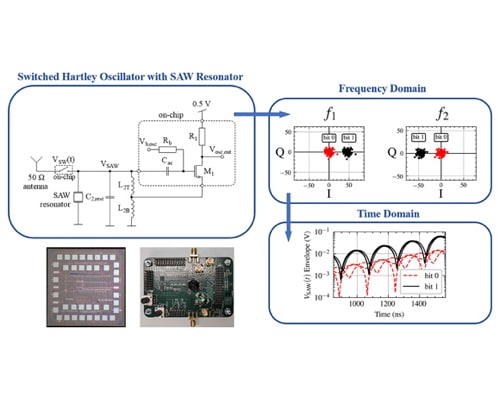

A novel wakeup receiver design is based upon a switched injection-triggered oscillator (SITO) with a surface acoustic wave (SAW) resonator for two modes of oscillation. The SAW resonator in parallel with a Hartley oscillator is disconnected from the antenna at sampling times to simultaneously achieve extremely low DC energy consumption per bit and very high sensitivity.

Noise analysis applies a new two-resonator model with three components: 1) Noise accumulated in the SAW resonator during the charge phase, 2) Super-regeneratively amplified noise before opening the antenna switch, and 3) Super-regeneratively amplified noise after opening the antenna switch.

Application

Wakeup receiver with extremely low DC power consumption

Performance

65 pJ/bit improves energy efficiency state of the art by 4.3x when reported.

2 nW DC power consumption at 10 bps, 3.9 µW at 32 kbps.

-93 dBm measured input sensitivity, 136 kHz 3 dB bandwidth input filter, 165 dB figure of merit (FOM).