InP DHBT Linear Modulator Driver With a 3-Vppd PAM-4 Output Swing at 90 GBaud: From Enhanced Transistor Modeling to Integrated Circuit Design

Abstract

DOI: 10.1109/TMTT.2023.3305150

IEEEXplore: https://ieeexplore.ieee.org/document/10248949

Device

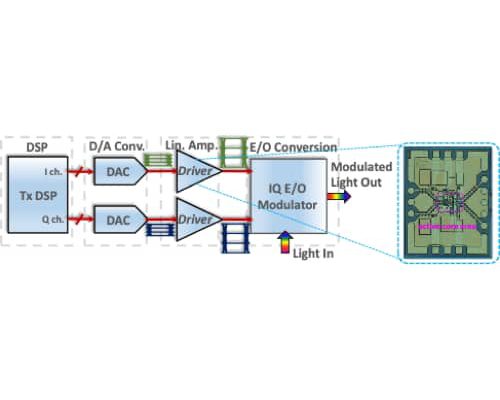

Indium phosphide (InP) double heterojunction bipolar transistor (DHBT) 90 GBaud linear modulator driver IC

Spectrum

380 GHz fT / 520 GHz fMAX

Novelty

1) 3-D EM-simulation DHBT de-embedding is used to improve DHBT modeling beyond 50-GHz for high-frequency IC design

2) Two-paralleled-transistor cascode differential pairs in the output stage of the linear driver optimizes the tradeoff between linear output swing, gain–bandwidth product, impedance matching, and power consumption using the “self-peaking” mechanism of the cascode stage.

3) Bandwidth extension using “self-peaking” technique is shown to be inherent to the cascode architecture and compatible with multiple technologies

Application

1THz/s/channel optical transceivers, beyond 5G/6G sub-terahertz power generation

Performance

> 110 GHz 3db bandwidth; 13 dB peaking gain at 95 GHz;

90 GBaud (180 Gb/s) using 4-level pulse amplitude modulation (PAM-4);

9.1 dB PO 1dB and 2.7% rms-THD at 3 VOppd output voltage swing;

0.67 W power consumed, 1.5 GBd FoM driver, 2.4 GBd FoM output stage