A 65-nm CMOS mm-Wave Blocker-Tolerant Digital Receiver Array

Abstract

DOI: 10.1109/TMTT.2025.3628958

IEEEXplore: https://ieeexplore.ieee.org/document/11239418

Device

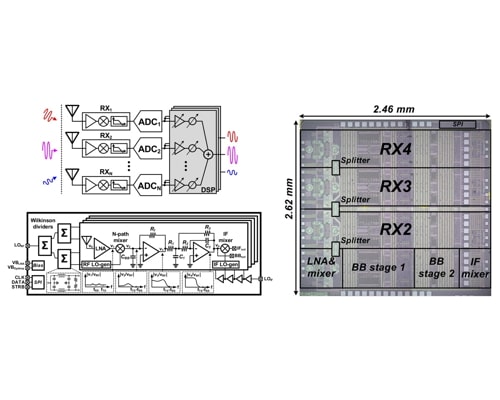

4-element blocker-tolerant digital receiver array in 65 nm CMOS technology.

Spectrum

22 – 31 GHz (28 GHz nominal)

Novelty

With a single amplification stage LNA, all RF and BB voltage nodes except the LNA’s input experience virtual ground in-band (IB) and filtering out-of-band (OOB), resulting in both high IB linearity and high blocker-induced compression performance (B1dB). LO leakage to the antenna is mitigated by the reverse isolation of the LNA.

The combination of a linear single-stage LNA followed by an N-path mixer with low input impedance across the frequency band also achieves low NF.

A baseband (BB) transimpedance amplifier (TIA) enhances linearity.

Application

5G and 6G communication systems.

Performance

<4-dB noise figure (NF) for each RX, 40 dB RX gain, -20 dBm in-band (IB) IIP3, −3.5-dBm B1dB at a 500-MHz offset;

−40-dB vector magnitude (EVM) error with modulated IB and OOB signals for−12-dBm blocker power;

±60◦ reception angle, signal-to-interference-and-noise ratio (SINR) improved from from−6 to 31 dB with spatial tolerance achieved with beam-nulling capability.