A 50-Gb/s 1.35-pJ/b PAM-4 VCSEL Transmitter With Three-Tap Asymmetric FFE and Current-Resue Technique in 40-nm CMOS

Abstract

DOI: 10.1109/TMTT.2024.3516072

IEEEXplore: https://ieeexplore.ieee.org/document/10813625

Device

50-Gb/s 1.35-pJ/b PAM-4 VCSEL transmitter with a three-tap asymmetric FFE in 40-nm CMOS

Spectrum

850 nm

Novelty

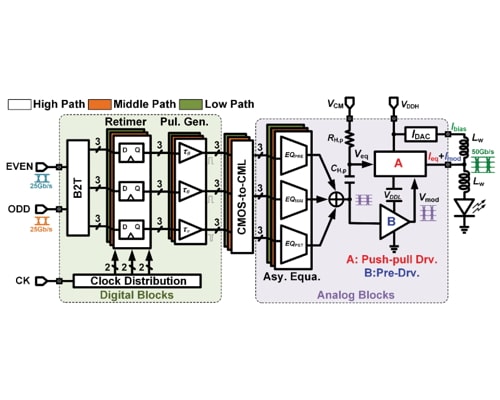

The signal equalization path incorporates a binary-to-thermal (B2T) coder with three-tap asymmetric feedforward equalization (FFE) for adjustable eye-height optimization.

Asymmetric feedforward equalization enhances the output driver's bandwidth by shifting the summation node to the equalizer output and addresses the VCSEL’s nonlinear light-current–voltage (L-I–V ) response.

The stacked output stage with a low- pass current reuse pre-driver and a high- pass push – pull driver enhances the efficiency by reusing the modulation current.

Application

Cost-effective high-speed data transmission for datacenters.

Performance

1.35 pJ/b at 50 Gb/s power efficiency with 3.3 V biased VCSEL.

2.4 dB extinction ratio (ER) when butt-coupled with a 2-m multimode fiber (MMF).

3.4 dBm optical modulation amplitude (OMA) at the 50-Gb/s PAM-4.