A 220-GHz Low-Noise CMOS Receiver Utilizing Noise Cancellation and Gain Enhancement

Abstract

DOI: 10.1109/TMTT.2025.3602475

IEEEXplore: https://ieeexplore.ieee.org/document/11148280

Device

Low-noise receiver implemented in a 40-nm bulk CMOS process with fT / fmax = 300/270 GHz.

Spectrum

220 GHz

Novelty

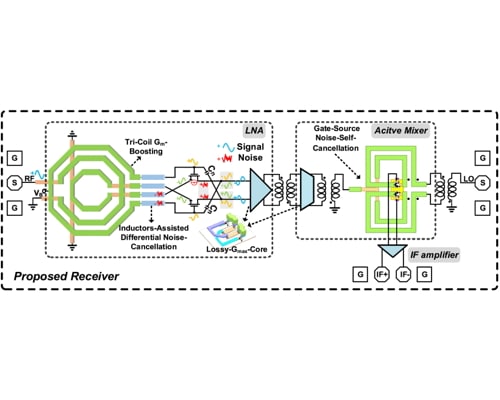

A tri-coil gm-boosting network and an inductor-assisted differential noise-cancellation network are proposed that improve both gain and noise performance. The lossy-Gmax-core architecture ensures simultaneous gain and noise matching and further enhances the gain, achieving the lowest reported noise figure among CMOS RXs operating above 200 GHz.

Application

Ultrahigh speed wireless communication systems.

Performance

17.8 dB conversion gain (CG); 11.8 dB minimum noise figure (NF); -24.7 dBm input 1-dB compression point (IP1dB).

35.5 mW DC power consumption; a core area of 0.078 mm2 RX core area and a 0.2 mm2 total area.