A 205-273-GHz Frequency Multiplier Chain (×6) with 9-dBm Output Power and 1.92% DC-to-RF Efficiency in 0.13-μm SiGe BiCMOS

Abstract

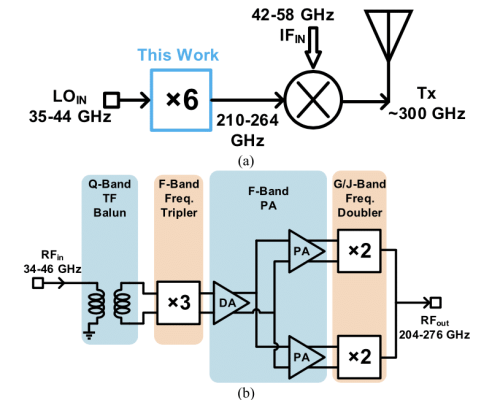

This paper presents a 205-273 GHz wideband frequency multiplier chain (FMC) in a 0.13-μm SiGe BiCMOS technology with fT/fmax = 300/500 GHz. The proposed FMC consists of a Q-band input transformer (TF) balun, an F-band frequency tripler, an F-band power amplifier (PA), and a G/J -band frequency doubler, which results in a 6th multiplier. To obtain high output power and high efficiency, a two-way power combining push-push doubler with second harmonic resonators is introduced. The high Q-factor cross-fingers capacitor is employed in the wideband output matching network to reduce the insertion loss. A wideband PA is utilized to drive the following doubler. The frequency tripler with an adaptive bias circuit is proposed to exhibit high output power while relatively flat conversion gain (CG), with which, the output power of the tripler can be easily controlled. An analysis of the input TF balun is introduced for improving the common mode rejection, which results in high even harmonic suppression of the tripler. The proposed FMC exhibits 9-dBm saturated output power (Psat), with a 3-dB bandwidth of 68 GHz. The DC-to-RF efficiency of 1.92% is achieved with more than 10 dB CG at 252 GHz. The FMC consumes less than 0.5 W and occupies a small chip area. To the best of our knowledge, the proposed FMC exhibits the highest Psat and DC-to-RF efficiency in silicon-based implementations beyond 200 GHz.

https://ieeexplore.ieee.org/document/10032257