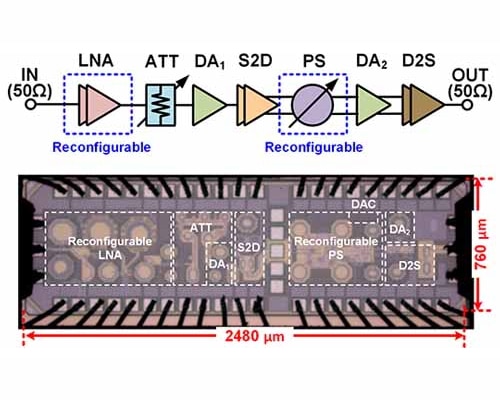

A 2–18-GHz Reconfigurable Phased-Array Receiver Front-End in 65-nm CMOS

Abstract

DOI: 10.1109/TMTT.2025.3596492

IEEEXplore: https://ieeexplore.ieee.org/document/11128915

Device

An ultra-wideband reconfigurable phased array receiver (RX) front-end in TSMC 65-nm CMOS technology.

Spectrum

2–18 GHz

Novelty

A reconfigurable phase shifter (PS) with reconfigurable resistor-capacitor (RC)- resistor-inductor (RL)-RC polyphase filter (PPF) I/Q generator performs dual-band switching and reduces the gain-phase error.

A reconfigurable low-noise amplifier (LNA), based on a reconfigurable feedback network (RCFN) and a reconfigurable load network (RCLN), ensures a consistently low and flat noise figure (NF) and extends the gain BW.

Application

Phased-array beamformers for wideband phased-array radars and next-generation millimeter-wave (mm-Wave) wireless communication systems.

Performance

2.6 dB to 4 dB NF; 0.4° to 3.3° rms phase error from 2 to 18 GHz;

−29.6 to −26.7 dBm input 1 dB compression point (IP1 dB);

132 mW power consumption.