An Oscillator-Free LO Generator for Beyond 5G Wireless Communication Systems

Abstract

DOI: 10.1109/TMTT.2025.3568403

IEEEXplore: https://ieeexplore.ieee.org/document/11010894

Device

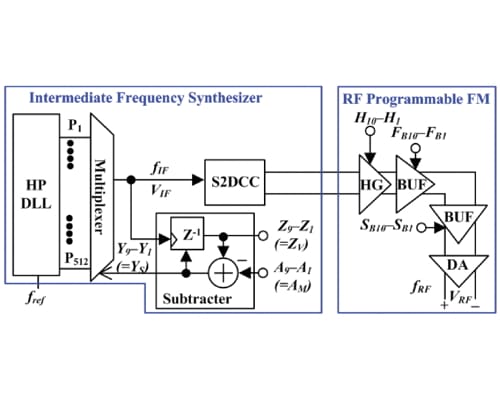

Cascade synthesizer topology consisting of a 512-phase delay-locked loop (DLL) IF synthesizer with a 512-to-1 multiplexer and an RF programmable frequency multiplier (PFM) in 65-nm CMOS technology

Spectrum

1.25 GHz - 5.0 GHz

Novelty

A novel cascade topology of a DLL-based IF synthesizer followed by a programmable RF frequency multiplier is proposed for LO-free frequency generation with ultra-low input phase noise. This approach is an improvement to the prevailing low phase noise multiplying delay-locked loop architectures that overcomes the constraint of having to physically change the delay unit (DU) of a voltage-controlled delay line (VCDL) to change the output frequency.

Application

Oscillator-free LO generator for 5G and beyond wireless communication systems

Performance

4.9 – 45.05 MHz channel resolution range which is significantly finer that the reference frequency; 120% output frequency BW;

32 fs integrated RMS jitter from 1 kHz to 100 MHz for 5 GHz output;

-257.1 to -292.1 figure of merit (FoM) depending on the method to calculate;

17.1 mW power consumption, 0.68 mm2 die size