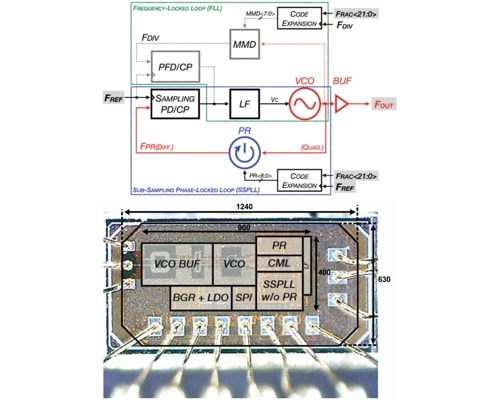

A 27.2–31.2 GHz 92-fs rms Integrated Jitter, Fractional-N Subsampling PLL Using Phase Rotating Technique in 65-nm CMOS

Device

Phase rotation (PR) based fractional N-subsampling phase locked loop (FN-SSPLL) in 65-nm RF CMOS

Spectrum

27.2-31.2 GHz

Novelty

Dithering the feedback signal to the VCO and employing a sigma-delta modulator (SDM) on the PLL increases the resolution of the output frequency.

Performance

24 Hz frequency resolution; -104.67 dBc/Hz phase noise at 400 kHz offset at 29.1 GHz; 92 fs rms jitter from 1 kHz to 10 MHz.