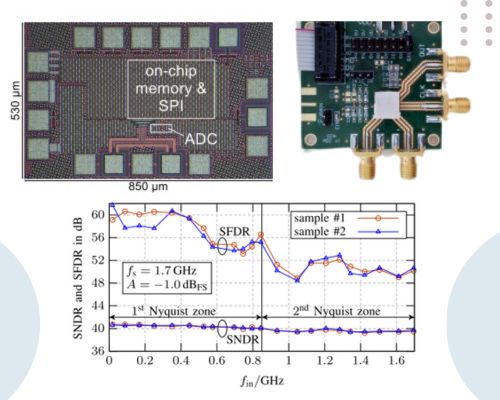

A 1.38-mW 7-bit 1.7-GS/s Single-Channel Loop-Unrolled SAR ADC in 22-nm FD-SOI With 8.85 fJ/Conv.-Step for GHz Mobile Communication and Radar Systems

Device

A 7-bit single-channel loop-unrolled successive approximation register (SAR) analog-to-digital converter (ADC)

22-nm fully depleted silicon on insulator (FDSOI)

Novelty

Tuning to the FDSOI back-gate voltage to calibrate the comparator offset reduces power dissipation 5% and noise 10% compared to conventional approaches.

Sharing reset transistors among memory cells reduces delay between comparator decision and switching by 15%.

Application

Ultrawideband (UWB) receivers, phase-modulated continuous wave (PMCW) radar

Performance

Power consumption is 1.38 mW

Sampling rate is 1.7 GS/s

Waldon figure of merit (FoMW) is 8.85 fJ/Conv-Step

Effective number of bits is 6.52