8.0 pJ/bit BPSK Transmitter with LO Phase Steering and 52 Gbps Data Rate Operating at 246 GHz

Abstract

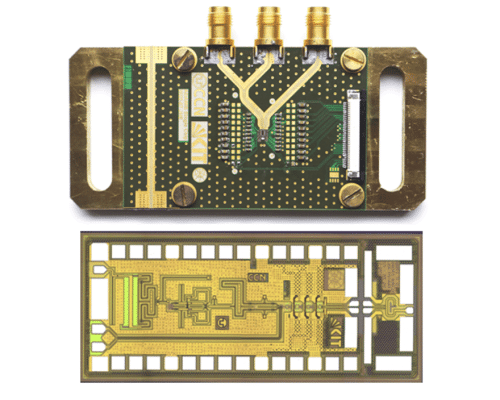

This work investigates a broadband binary phase-shift keying (BPSK) transmitter system with a measured data rate of 52 Gbps and 8.0 pJ/bit transmitter efficiency. The transmitter features local oscillator (LO) multiplication, 360° LO phase steering for phased array applications, a power-efficient BPSK modulator, and a very compact power amplifier connected to a differential bond wire interface. By employing a low-order modulation scheme, the baseband chain can be implemented at a very low complexity, which benefits power consumption. Proving the concept, an integrated circuit is fabricated in a 130-nm silicon–germanium (SiGe) bipolar complementary metal–oxide–semiconductor (BiCMOS) technology with a ft/fmax of 350/ 450 GHz, covering 1.158 mm2 . At 52 Gbps, this circuit shows the highest reported data rate using BPSK modulation. The saturated output power of 3.5 dBm, while consuming 414 mW of direct-current (DC) power, results in a radio-frequency (RF) efficiency of 0.54%, which is a 28% improvement versus the state-of-the-art. The high achieved data rate combined with circuit modules optimized for low power consumption results in a measured transmitter efficiency of 8.0 pJ/bit, improving the state of the art of complete transmitter systems in the same frequency band by 68% and 46% compared to BPSK and quadrature phase-shift keying (QPSK) systems respectively.

https://ieeexplore.ieee.org/document/10034795