-

Wednesday, November 17, 2021 6:30 pm - 8:00 pm(Los Angeles Time) Add to my calendar

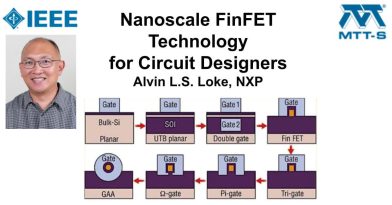

Nanoscale FinFET Technology for Circuit Designers

Dr. Alvin Loke

NXP Semiconductors

Abstract: CMOS scaling maintains economic relevance with 5nm SoCs already available in consumer products for a year now and 3nm deep in product development. Modest feature size reduction and design/technology innovations co-optimized for logic and SRAM scaling continue to offer compelling node-to-node power, performance, area, and cost benefits. In this tutorial, we start with a brief history of transistor evolution to motivate the migration from planar to the fully depleted FinFET. We will summarize the key process technology elements that have enabled the finFET CMOS nodes, highlighting the resulting device technology characteristics and challenges impacting design. To address the growing effort required for physical design closure, we cover design strategies including density-friendly layout, continuous active area layout, and template-based analog cells. We conclude with a discussion of what remains in finFET development and a peek at transistor architectures on the horizon.

Speaker’s Bio: Alvin Loke recently joined NXP Semiconductors as a Technical Director in San Diego, having worked on CMOS nodes spanning 250nm to 2nm at Agilent, AMD, Qualcomm, and TSMC. He received a B.A.Sc. degree with highest honors from the University of British Columbia, and M.S. and Ph.D. degrees from Stanford University. Upon graduating, he spent several years in CMOS process integration. Since 2001, he has worked on analog/mixed-signal design focusing on a variety of wireline links, design/model/technology interface, and analog design methodologies. He has been an active IEEE Solid-State Circuits Society (SSCS) volunteer since 2003, having served as Distinguished Lecturer, Custom Integrated Circuits Conference (CICC) Committee Member, Webinar Chair, Denver and San Diego Chapter Chair, and Guest Editor for Journal of Solid-State Circuits and Solid-State Circuits Letters. He currently serves in the SSCS AdCom and VLSI Symposium committees, and as SSCS Chapters Chair and San DIego Joint MTTS Chapter Vice Chair. Alvin has authored over 60 publications (including the CICC 2018 Best Paper; invited ISSCC, VLSI Symposium, BCICTS short courses; and ICICDT keynote) and holds 29 US patents.

This event is organised by IEEE MTT-SCV.