-

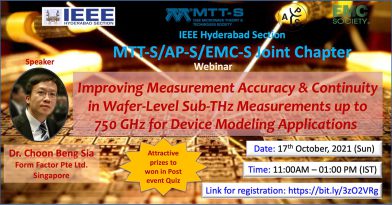

Sunday, October 17, 2021 11:00 am - 1:00 pm(New Delhi Time) Add to my calendar

Improving Measurement Accuracy and Continuity in Wafer-Level Sub-THz Measurements up to 750 GHz for Device Modelling Applications

Dr. Choon Beng Sia

Form Factor Pte Ltd., Singapore

Abstract: Achieving accurate and continuous S-parameters measurements for sub-THz wafer-level device characterization is particularly important for device modelling applications. Accurate measurements allow accurate device SPICE models to be developed, which in turn help to facilitate efficient and cost-effective one-pass RFIC circuit design success. This talk discusses the various challenges affecting measurement continuity and accuracy at such high frequencies. A sub-THz measurement strategy with pre-calibration check for low probe contact resistance, combining power and S-parameter probe tip calibration, implement-ing post-calibration verification checks and ensuring consistent and accurate DC biasing of devices across all frequency bands, will be presented to improve the measurement continuity and quality of wafer-level measurements up to 750 GHz.

Speaker’s Bio: Dr Choon Beng Sia is a SSG Fellow, conferred by the President of the Republic of Singapore. He is also a Nanyang Research Scholar and has received doctorate degree in Electronics Engineering from Nanyang Technological University, Singapore with 6 tier-1 journals & 3 conference papers published for his Ph.D. dissertation on RF Design, Characterization and Modelling of Silicon-based Devices. In his current work at FormFactor as a Test Technologist, Dr Sia develops solutions to overcome semiconductor wafer test and measurement challenges. His research interests include design, test and modelling of siliconbased RF devices, THz calibration and measurements for 5G and IoT applications, photonics and power device wafer tests for LIDAR/Autonomous Transport/Optical communication applications as well as applying data analytics, deep learning and artificial intelligence to wafer tests and device modelling. Dr Sia serves in the IEEE MTT-3 technical committee that develops standards and best practices for RF measurements and he is also the MTT-3 speaker bureau specialising in wafer RF and 5G tests. He lectures graduate-level semiconductor courses for IEEE and Singapore Semiconductor Industry Association. Through SPRING, the Singapore National Standards board, Dr Sia represents Singapore as a Technical Expert in various IEC technical committees, developing standards for MEMs, optical and wafer-level reliability tests for semiconductor devices. A wafer test, device modelling and process design kit (PDK) expert, Dr Sia is often consulted by international semiconductor companies, defence, government and medical research institutes. He is a frequent invited speaker and organizer of IEEE workshops, international test forums and presently holds 12 international patents. Dr Sia has published more than 50 scientific journals and conference publications, of which 85% of them as the first author. His technical papers on 5G production wafer test received multiple “Best Paper” awards and the “Best ATE Paper” award at the 2018, 2019 Semiconductor Wafer Test Conference and 2020 Test Vision Symposium, while his paper on Silicon Photonics wafer test received the “Most Inspirational Paper” award at the 2019 Semiconductor Wafer Test Conference.

This event is organised by MTT/AP/EMC Joint Chapter, IEEE Hyderabad Section.